Каким должен быть хороший RISC процессор? Как вам такая схема? Насколько такой процессор будет производительным?

Процессор должен иметь команды 2 типов.

- Память-регистр. Считывание из памяти в регистр и запись из регистра в память.

- Операции между регистрами.

Так же процессор должен иметь 255 регистров общего назначения и ширину шины памяти для обмена с кэшем в 2048 бит, то есть 2 килобайта.

Таким образом каждая команда это квартет 8 битных кодов.Первый код означает тип вычислительного блока. Второй, третий и четвёртый содержат номера 64 разрядных регистров которые будут подключены ко входам и выходам блока. Всего их максимум 3.

Для работы с дробными и целыми числами которые имеют длину 128 бит, шина между регистром и блоком имеет ширину 128 бит. Первые 64 бита берутся из указанного регистра, а вторые 64 бита берутся из следующего по счёту.

Последовательно записанные в памяти команды будут на этапе компиляции разделены нулевым оператором. Все команды находящиеся между 2 нулевых операторов по возможности будут выполнены одновременно с максимальным использованием доступных функциональных блоков и селекторов.

Переход в функцию, будет сопровождаться записью регистров в кэш по широкой шине за один такт, и переходом адреса исполнения по паре регистров адреса и смещения. Возврат будет выполняться считыванием в регистры значений обратно из стека по широкой шине, за исключением тех бит которые которые обозначены битовыми масками в 2 парах регистров (итого 256 бит).

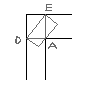

Дабы упростить переключатели ввода-вывода операционных блоков, их следует сделать 8 ступенчатыми.

Так же у процессора должна быть явная команда подготовки перехода, то есть память по возможному адресу перехода будет помещаться в кэш пока процессор проводит условные операции.

Естественно порядок выполнения команд и расстановка нулевых операторов осуществляется компилятором.

Так же в процессоре должна быть аппаратная поддержка циклов.