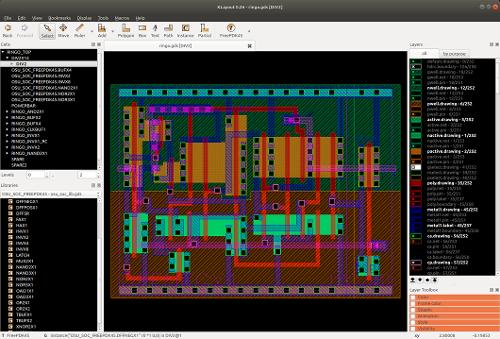

На этой неделе, 10 сентября, после двух лет разработки вышла следующая версия САПР топологий интегральных микросхем (ИМС) KLayout. Данная кроссплатформенная САПР написана на С++ с использованием тулкита Qt, распространяется на условиях лицензии GPLv2. Имеется также функция просмотра файлов топологий печатных плат в формате Gerber. Поддерживаются расширения на Python и Ruby.

Основные изменения релиза 0.26

- Добавлена проверка соответствия топологии и схемы (Layout vs. Schematic — LVS ) и экстракция списка цепей из топологии;

- Улучшена проверка правил проектирования Design Rules Check (DRC);

- Добавлена проверка топологии на наличие паразитных антенн (Antenna check);

- Добавлен браузер библиотек;

- Исправлены баги;

>>> Подробности